|

|

||||||||||||||

|

||||||||||||||

| TEXT:鈴木雅暢 | ||||||||||||||

|

||||||||||||||

|

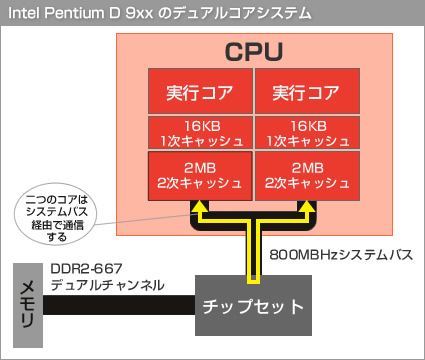

||||||||||||||

| Intelが絶対の自信を持って投入するCore 2 Duo。その高性能、低消費電力の秘密は新マイクロアーキテクチャ「Intel Coreマイクロアーキテクチャ」にある。 Intel Coreマイクロアーキテクチャは、モバイル向けCPUであるPentium MのBanias/Dothanコア、そしてその後継のCore Duoで採用されたYonahコアの流れを継承しつつ、より発展させたものだ。これまでPentium 4/Pentium D系が採用してきたNetBurstマイクロアーキテクチャでは、動作クロックを高速化することでパフォーマンスを向上させることを目指していたが、Coreマイクロアーキテクチャでは、マルチコアを前提とした上で、電力効率とのバランスを重視し、クロックあたりの性能をいかに向上させるかといった方向へと向かっている。 その具体的な特徴として、Intelは以下の五つの機能を挙げる。 ・ワイド・ダイナミック・エグゼキューション ・アドバンスド・スマート・キャッシュ ・アドバンスド・デジタルメディア・ブースト ・スマート・メモリー・アクセス ・インテリジェント・パワー機能 もっとも影響が大きいと思われるのが「ワイド・ダイナミック・エグゼキューション」。Pentium Pro(P6)以降のx86 CPUは、x86命令をRISC風の命令(μOP)に変換して複数のパイプラインでアウトオブオーダー実行(プログラムに記述された順序によらず、実行できる命令から実行していく手法)することで高クロック動作を可能にしてきた。この変換を行なうデコーダと命令実行パイプラインはP6当初から三つであったが、ワイド・ダイナミック・エグゼキューションでは四つへ拡張。さらに、特定の条件を満たした二つのx86命令を一つの命令として扱う「マクロ・フュージョン」により、最大五つのx86命令を同時実行できるようにした。つまり、一つのサイクルで実行できる命令の数(x86命令換算)を、従来の三つから最大五つへと増やしたわけだ。実際に計算を行なう演算器(ALU)も、Yonahコアの二つから三つへと増やしている。 「アドバンスド・スマート・キャッシュ」は、二つのコアで共有する2次キャッシュに関する機能で、Core Duoで導入されているスマート・キャッシュの発展型。Pentium DやAthlon 64 X2ではコアごとにそれぞれ独立して2次キャッシュを持っているが、Coreマイクロアーキテクチャでは、二つのコアで一つの2次キャッシュを共有する。二つのコアで同じメモリ内容をキャッシュしている場合に、独立キャッシュではCPU間で通信し、内容の同一性を保つ作業が必要だが、共有キャッシュではそれが不要だ。また、二つのコアがまったく違うアドレスをキャッシュするような場合、二つのコアで容量を等分せず、3MB+1MB(4MBの場合)といった柔軟な割り当てが可能だ。さらに今回は、1次キャッシュ←→2次キャッシュの転送速度を2倍に拡張しているのも特徴だ。 「アドバンスド・デジタルメディア・ブースト」は、ALUを128bit化したことにより、128bitレジスタを利用するSSE系の命令を1クロック(従来は2クロック)で実行できるようにした。これにより、SSE系命令の実効性能が格段に改善することが予想される。 また、「スマート・メモリー・アクセス」は、メモリのロード/ストアをインテリジェントに分析し、アウトオブオーダー実行、および効果的なプリフェッチを行なうことでレイテンシを隠蔽する機能だ。 そして、「インテリジェント・パワー機能」は、消費電力を削減するための機能。コア内部の電力管理を徹底し、使われていないユニットの電力をより積極的にOFFにする。Pentium M以降のモバイルCPUにも同様の機能はあるが、バス幅のうちデータ転送で使われていない部分を切り離すスプリット・バスの導入など、より監視を細分化し、低消費電力化を推し進めたものである。 |

||||||||||||||

|

||||||||||||||

| 左がPentium D 960、右がCore 2 Duo。ヒートスプレッダで覆われた表面はほとんど何も変わらない。裏面のチップコンデンサ/チップ抵抗の配置には若干変化が見られ、Core 2 Duoではコンデンサが片側にまとめて配置されている | ||||||||||||||

対応するソケットはLGA775だが、Core 2 Duoは要求するVRMの仕様が変更されたため、従来のマザーボードの流用はほとんどできない 対応するソケットはLGA775だが、Core 2 Duoは要求するVRMの仕様が変更されたため、従来のマザーボードの流用はほとんどできない |

||||||||||||||

|

||||||||||||||

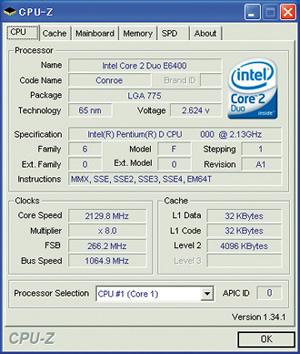

| 以上がCore 2 Duoが採用するIntel Coreマイクロアーキテクチャの特徴だ。これからは、より具体的なCore 2 Duoの仕様を見てみよう。 現状で分かっている公式情報としては、65nmプロセスルールで製造され、共有2次キャッシュの容量は900番台のPentium Dと同じ4MBということ。そして、64bit拡張技術のEM64T、負荷に応じてクロックと電圧を変更する拡張版SpeedStep(EIST)もサポート。従来のPentium Dと同様のLGA775パッケージで提供される、といったところ。7月にIntelが2.93GHzのCore 2 Extremeを市場に投入することは発表されているが、そのほかの動作クロックやプロセッサ・ナンバなどの正確なラインナップは現状では不明である。 今回入手したCoreマイクロアーキテクチャのCPUは外観はLGA775パッケージのPentium Dとほとんど変わらない。実際にその情報をCPU-Zで確認してみると、「Core 2 Duo E6400」と表示され、動作クロックは2.13GHzと表示された。システムバスクロックは1,066MHz。Pentium Dの800MHzから33%ほど拡張されている。 また、YonahコアのCore Duoと比べると、EM64T(64bit拡張)のほかに、SSE4のフラグが立っているのが興味深い。これについては正式な情報はなく、前述の「アドバンスド・デジタルメディア・ブースト」のサポートをSSE4と表示させているのか、追加命令があるのかは不明だ。何よりも気になる性能と消費電力は次ページで検証していく。 |

||||||||||||||

|

||||||||||||||

|

||||||||||||||

| Coreマイクロアーキテクチャでは、命令デコーダや実行パイプラインなどを4命令同時実行構造へと拡張。二つのx86命令を一つの命令として扱うマクロ・フュージョンが機能する場合は、実質5命令実行となる。2次キャッシュは共有型のため、キャッシュの同一性を保つ作業は不要で、各コアが使える容量も柔軟な割り当てが可能だ | ||||||||||||||

|

||||||||||||||

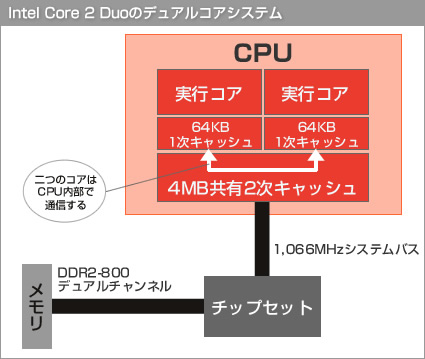

| コアの純粋な性能を計測するテストだが、Integer x8 iSSE2、Floating-Point x4 iSSE2でCore 2 Duoが爆発している。アドバンスド・デジタルメディア・ブーストによってSSE性能が格段に上昇していることが分かる。SSE4対応アプリケーションの登場が楽しみだ | ||||||||||||||

|

||||||||||||||

CPU-Z(Ver.1.34.1)での表示画面。EM64T(64bit拡張)のほかに、SSE4のフラグが立っている。SSE4の詳細は不明だが現時点でのCPU-Zではこのように表示される CPU-Z(Ver.1.34.1)での表示画面。EM64T(64bit拡張)のほかに、SSE4のフラグが立っている。SSE4の詳細は不明だが現時点でのCPU-Zではこのように表示される |

||||||||||||||

|

||||||||||||||

|

|

サイト内検索

DOS/V POWER REPORT 最新号

-

-

DOS/V POWER REPORT

2024年冬号発売日:12月28日

特別定価:2,310円

書籍(ムック)

-

PC自作・チューンナップ虎の巻 2023【DOS/V POWER REPORT特別編集】

発売日:2022/11/29

販売価格:1,800円+税

-

このレトロゲームを遊べ!

発売日:2019/05/29

販売価格:1,780円+税

-

特濃!あなたの知らない秋葉原オタクスポットガイド

発売日:2019/03/25

販売価格:1,380円+税

-

わがままDIY 3

発売日:2018/02/28

販売価格:980円+税

-

忍者増田のレトロゲーム忍法帖

発売日:2017/03/17

販売価格:1,680円+税

-

楽しいガジェットを作る いちばんかんたんなラズベリーパイの本

発売日:2016/09/23

販売価格:2,400円+税

-

DVDで分かる! 初めてのパソコン自作

発売日:2016/03/29

販売価格:1,480円+税

-

ちょび&姉ちゃんの『アキバでごはん食べたいな。』2

発売日:2015/12/10

販売価格:1,280円+税

-

髙橋敏也の改造バカ一台&動く改造バカ超大全 風雲編

発売日:2015/06/29

販売価格:2,500円+税

-

髙橋敏也の改造バカ一台&動く改造バカ超大全 怒濤編

発売日:2015/06/29

販売価格:2,500円+税

-

わがままDIY 2

発売日:2015/02/27

販売価格:980円+税

-

ちょび&姉ちゃんの『アキバでごはん食べたいな。』

発売日:2014/12/05

販売価格:1,280円+税

-

-

わがままDIY 1

発売日:2011/12/22

販売価格:980円+税

アンケートにお答え頂くには「CLUB IMPRESS」への登録が必要です。

*プレゼントの対象は「DOS/V POWER REPORT最新号購入者」のみとなります。

ユーザー登録から アンケートページへ進んでください