|

|

| TEXT:鈴木雅暢 |

|

|

|

ついに登場、Yorkfield!

45nm世代で勢力図はどう変わる? |

|

|

クアッドコアの“本命”とも目されていたYorkfieldコアのCore 2 Quadがついに登場。これをきっかけにクアッドコアCPUのさらなる普及が期待できるが、性能とは別の部分で問題も浮上している。 クアッドコアの“本命”とも目されていたYorkfieldコアのCore 2 Quadがついに登場。これをきっかけにクアッドコアCPUのさらなる普及が期待できるが、性能とは別の部分で問題も浮上している。 |

|

|

|

|

|

| Intelが45nmプロセスルールのメリットとしてアピールするのが、High-k(高誘電率)ゲート絶縁膜とメタルゲート電極の採用によるリーク電流の大幅な低減だ。リーク電流とは、トランジスタのスイッチがOFFのときにも流れてしまう電流のことで、高クロック化や低消費電力化の障害となっていた。このリーク電流低減によって電力効率が上昇しており、従来より高クロックで発熱を小さくすることが可能となった。また、製造技術の微細化の基本的なメリットとして、トランジスタ一つ一つを小さく作ることができ、単位面積あたりに多数のトランジスタを集積することができることも挙げられる。これは大容量2次キャッシュの搭載につながっている。 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| ■ |

45nmプロセスルールを採用した3モデルの新クアッドコア |

|

|

IntelのCPUラインナップに、新しくCore 2 Quad Q9000シリーズが追加された。これは開発コードネーム「Yorkfield(ヨークフィールド)」の名で呼ばれていたもので、1月中旬にデビューした「Wolfdale(ウルフデール)」ことCore 2 Duo E8000と同じ45nmプロセスルールで製造されている。「Wolfdale」のダイを二つ接続することでクアッドコアとしているのは、65nm世代のデュアルコア(Conroe:コンロー)とクアッドコア(Kentsfield:ケンツフィールド)の関係と同様だ。

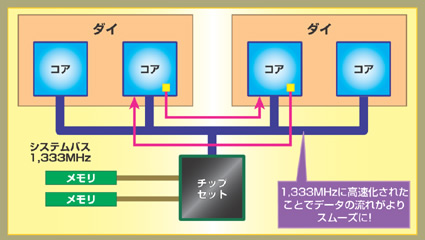

今回、Core 2 Duo Q9000シリーズとして追加されたのは、動作クロック2.83GHzのCore 2 Quad Q9550、同2.66GHzのQ9450、同2.5GHzのQ9300の3モデル。いずれもシステムバスは1,333MHzと、従来のQ6000シリーズの1,066MHzから拡張されており、上位2モデルは、2次キャッシュ容量も12MB(6MB×2)と1.5倍に増えている。TDPは共通で95Wである。

この45nm世代のCPUのマイクロアーキテクチャは「“Enhanced”Core MicroArchitecture」と呼ばれるように、65nm世代からマイナーチェンジされている。従来の約2倍の割り算性能を持つRadix-16除算器の搭載、Intel Virtualization Technologyの効率化、SSEデータの並べ換えを高速にするSuper Shuffle Engineの導入、新拡張命令であるSSE4.1のサポートなどが主な内容である。

各モデルの実売価格は別掲のとおりでこれだけ見るとCore 2 Quad Q9450などはかなり買い得感が高く、またクアッドコアが盛り上がりそうな予感もするのだが、現実的には難しいかもしれない。と言うのも、WolfdaleコアのCore 2 Duoは2月後半から品薄が続いているが、このYorkfieldコアのCore 2 Quadはそれ以上に流通量が少なく、販売開始当初から深刻な品薄となっている。3月15日に行なわれた「Windows Vista Ultimate SP1 Σ発売記念イベント」に出席したIntelの天野氏は、プレゼンテーションの中でこの出荷状況について言及し、改善されるまでにはもう少し時間がかかるという見通しを述べている。残念ながら、しばらくはもどかしい状況が続きそうだ。 |

|

|

|

| Intel |

|

|

|

Core 2 Quad Q9000シリーズ |

|

|

Intelのラインナップに新しく加わったクアッドコアCPU。システムバスが従来のQ6000シリーズの1,066MHzから1,333MHzに拡張されており、上位2モデルは、2次キャッシュ容量も12MB(6MB×2)と従来の1.5倍に増えている。ほかの45nm世代の製品と同様、CPU内部構造もわずかに変更されており、新命令のSSE4.1にも対応している。 Intelのラインナップに新しく加わったクアッドコアCPU。システムバスが従来のQ6000シリーズの1,066MHzから1,333MHzに拡張されており、上位2モデルは、2次キャッシュ容量も12MB(6MB×2)と従来の1.5倍に増えている。ほかの45nm世代の製品と同様、CPU内部構造もわずかに変更されており、新命令のSSE4.1にも対応している。 |

|

SPECIFICATION

CPUソケット:LGA775

コア数:4

製造プロセス:45nm

省電力機能:EIST

TDP:95W

拡張命令:SSE/2/3/4.1 |

|

|

| 製品名 |

周波数 |

コア数 |

2次キャッシュ |

| Core 2 Quad Q9550 |

2.83GHz |

4 |

6MB×2 |

| Core 2 Quad Q9450 |

2.66GHz |

4 |

6MB×2 |

| Core 2 Quad Q9300 |

2.5GHz |

4 |

3MB×2 |

|

|

| 製品名 |

3次キャッシュ |

システムバス |

予想販売価格 |

| Core 2 Quad Q9550 |

- |

1,333MHz |

63,000円前後 |

| Core 2 Quad Q9450 |

- |

1,333MHz |

38,000円前後 |

| Core 2 Quad Q9300 |

- |

1,333MHz |

32,000円前後 |

|

|

|

|

|

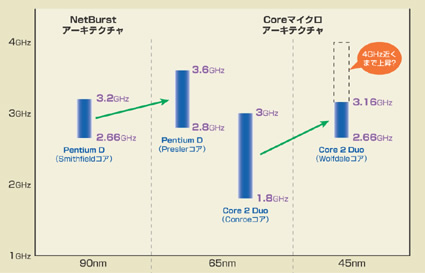

Core 2 Quad Q9000シリーズとQ6000シリーズの違いを改めて見てみよう。まずは動作クロックが全体的に向上したこと。これまでのCore 2 Quad Q6700は2.66GHzだったが、Q9550では2.83GHzに引き上げられている。動作クロックはもっとも分かりやすく性能に反映される要素だ。マイクロアーキテクチャが同じでクロックが向上すれば、ほぼどんなアプリケーションでも確実に速くなる。この動作クロックの高速化に貢献しているのが、45nmプロセスルールである。

プロセスルールとは製造技術の世代を表わす名称。「~nm」で示される数値が小さいほどトランジスタ一つ一つが小さく、単位面積あたりに多数のトランジスタを集積することができる。多くの場合、微細化とともに新素材や配線技術の改良なども行なわれていることが多く、Intelでもそのような製造技術全般の世代を示す言葉として使っている。そして、このIntelの45nmプロセスルールでは、High-k(高誘電率)ゲート絶縁膜とメタルゲート電極を採用することでリーク電流の大幅な低減に成功しているのが特徴だ。電力効率が上昇しており、消費電力を据え置いたままこれまで以上の高クロック化ができるようになった。

ちなみに、45nmプロセスルールで製造される半導体のどの部分が45nmかと言えば、実際の半導体上はどこも45nmではない。この45nmとは、リソグラフィ(回路パターンを焼き付ける露光装置)における設計上のゲート長が45nmということである。「設計上の」と回りくどい言葉を使うのは、シリコンウエハーへのドーピング技術などの関係上、リソグラフィとそれによってできあがる半導体のゲート長のサイズのズレ(45nmのリソグラフィを使って製造される半導体のゲート長は45nmよりも短い)が微細化とともに大きくなってきたからである。 |

|

|

|

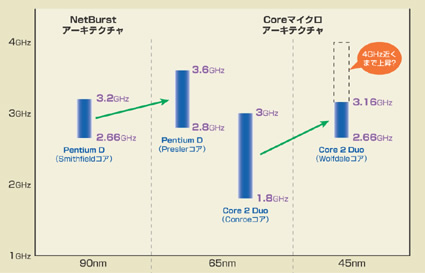

| 着実に進む高クロック化 |

|

|

|

| Intelのレギュラーモデルの動作クロックをグラフにしたもの。90nm世代から65nm世代、65nm世代から45nm世代と、プロセスルールの微細化に伴って同一アーキテクチャの相対的な動作クロックは上昇している |

|

|

|

|

|

|

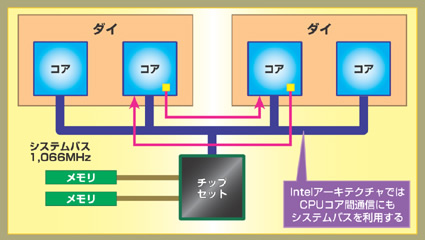

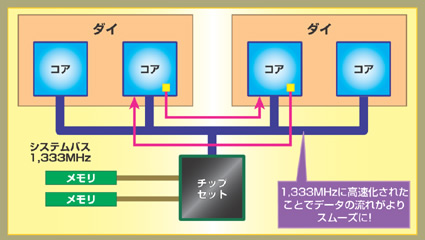

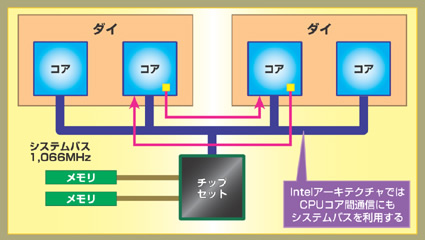

システムバスの速度が1,333MHzに向上したのも見逃せないトピックだ。デュアルコアのCore 2 Duoは、2007年夏に発表されたモデルから1,333MHz化されている。システムバスとは、CPUとチップセットを結ぶバスのことで、システムバスが高速化するということは、CPUとチップセットとのデータのやり取りがより高速にできることを意味する。このシステムバスを高速化する意味は、主にチップセットの先にあるメモリとのデータのやり取りの高速化にある。

CPUは計算に使うデータを外部の記憶装置(メモリ)から読み出すため、CPUが高速になればなるほどその計算に使うデータも速くCPU送り込む必要がある。それがシステムバスを高速化する理由だ。実際、数年前まではシステムバスの高速化は、はっきりメリットが表われる要素であった。しかし、データのプリフェッチなどインテリジェントなキャッシュ制御機能を備えるCore 2 Duoでは、システムバスの高速化効果があまり表面化せず、それほど重要な要素だと見られなくなってきている。

もっとも、クアッドコアCPUの場合は、デュアルコアCPUよりは、高速化効果が期待できる要素はある。クアッドコアの四つのコアがフル回転するとすれば、内部の演算性能はデュアルコアの2倍近くなるわけで、理屈上はシステムバスの速度もデュアルコアの2倍必要になるわけだ。システムバスがボトルネックになって内部の演算性能にデータ供給が追い付かないという状況は、当然デュアルコアよりもクアッドコアのほうが起こりやすい。そういう状況下では、システムバスが1,066MHzから1,333MHzに拡張されることによってボトルネックが緩和され、システム性能が高速化するという結果が期待できる。

また、IntelのクアッドコアCPUの場合は、デュアルコアのダイを二つ貼り付けてクアッドコアとしているため、一つのダイ内にある二つのコア同士の通信は高速に行なえるが、ダイをまたぐコア間の通信はシステムバスを経由して行なう必要がある。この部分ではシステムバスの高速化はダイレクトに効いてくる。

コア間での通信が必要な理由の一つが、キャッシュメモリの同一性(コヒーレンシ)保持である。キャッシュメモリはCPUとメインメモリの間に配置される高速なメモリ。キャッシュメモリはCPUに近くて高速な順に1次、2次と階層が分かれている。二つのコアが2次キャッシュを共有しているCore 2 Duoでは同一性を保持する必要はないが、2ダイのクアッドコアでは、各ダイの2次キャッシュがキャッシュしているアドレスのデータ内容が一方のダイにあるコアによって書き換えられていないか互いにチェックし、必要であればメインメモリ経由で最新データをキャッシュし直すという作業が必要だ。実際のアプリケーション利用時にこのような例がどれだけ起こっているのかは分からないが、このような場合にシステムバスは高速であればあるほどロスが少ないことは間違いない。 |

|

|

|

| システムバス高速化はクアッドコアに有利! |

|

|

|

|

|

| 四つのコアがフル回転した場合、計算に使うデータはデュアルコアの2倍必要で、単純に考えればデュアルコアの2倍のスピードのシステムバスが必要。システムバスがボトルネックになる状態に陥る可能性はデュアルコアより高い。また、Intelのクアッドコアではダイ間の通信をシステムバス経由で行なうため、この部分でも高速化のメリットはあるはずだ |

|

|

|

|

クアッドコアの“本命”とも目されていたYorkfieldコアのCore 2 Quadがついに登場。これをきっかけにクアッドコアCPUのさらなる普及が期待できるが、性能とは別の部分で問題も浮上している。

クアッドコアの“本命”とも目されていたYorkfieldコアのCore 2 Quadがついに登場。これをきっかけにクアッドコアCPUのさらなる普及が期待できるが、性能とは別の部分で問題も浮上している。 Intelのラインナップに新しく加わったクアッドコアCPU。システムバスが従来のQ6000シリーズの1,066MHzから1,333MHzに拡張されており、上位2モデルは、2次キャッシュ容量も12MB(6MB×2)と従来の1.5倍に増えている。ほかの45nm世代の製品と同様、CPU内部構造もわずかに変更されており、新命令のSSE4.1にも対応している。

Intelのラインナップに新しく加わったクアッドコアCPU。システムバスが従来のQ6000シリーズの1,066MHzから1,333MHzに拡張されており、上位2モデルは、2次キャッシュ容量も12MB(6MB×2)と従来の1.5倍に増えている。ほかの45nm世代の製品と同様、CPU内部構造もわずかに変更されており、新命令のSSE4.1にも対応している。